# 論文 8-1-12

# 2002 전력전자학술대회 우수추천논문

# TMS320F240을 이용한 PWM 인버터 유도전동기 구동 시스템의 전도노이즈 저감을 위한 스위칭 기법

朴奎炫, 金利勳, 元忠淵, 金奎植, 崔世琓, 咸年根

A Switching Technique for Common Mode Voltage Reduction of PWM-Inverter Induction Motor Drive System Using TMS320F240

> Park Kyu-Hyun, Kım Lee-Hun, Won Chung-Yuen, Kım Gyu-Sik, Choı Se-Wan, and Hahm Nyon-Kun

#### 요 약

PWM 인버터에 의해 구동되는 유도전동기에 발생되는 고주파 커먼 모드 전압은 전도성 EMI, 전동기 접지전류, 베어링 전류 및 다른 원치 않는 결과의 주원인이 된다 인버터 제어의 무효벡터 스위칭 상태는 나머지 유효벡터 스위칭 상태에 비교하여 큰 커먼 모드 전압을 일으킨다 그러므로 이 논문은 커먼 모드 전압을 완화하는 스위칭기법을 다룬다 즉 정현파 PWM 기법을 기본으로 한 커먼 모드 전압 제거방법을 제안하였다. PWM 신호는 각각의 정현파 기준신호와 120°위상차가 나는 3개의 캐리어 파형과 비교하여 발생된다 시뮬레이션과 실험적 결과는 제안된 PWM 기법에서 커먼 모드 전압이 종래의 PWM 기법보다 약 66% 더 저감됨을 보였다.

#### **ABSTRACT**

High frequency common mode voltage produced by PWM inverter fed induction motor is a major cause of conducted EMI, creation motor ground currents, bearing currents and other harmful products. The zero switching states of inverter control invoke large in comparison with the non-zero switching state of inverter control. We proposed a common mode voltage reduction method based on sinusoidal PWM technique PWM signal are generated by comparing respective sinusoidal reference signal with three triangular carrier wave displaced of 120° Simulation and experimental result show that common mode voltages in the proposed PWM technique are reduced by approximate 66% more than conventional PWM technique

Key Words: Conducted EMI, Sinusoidal PWM, Common Mode Voltage

\*성균관대학교 전기공학과 교수 E-mail won@yurim skku ac kr 접수일자 2002 10 25 1차심사요청일 2002 11 1 2차심사요청일 2002 11.28 심사완료일 2003 1 24

#### 1. 서 론

최근에 유도전동기는 마이크로 프로세서의 발달괴 현대 제어이론의 적용으로 산업현장에 널리 보급되고 있다

또한, 고속 스위칭 소자의 발달로 전압형 PWM 인

버터의 스위칭 주파수가 증가하게 되어 고성능 전동기 제어가 가능하게되었다 그러나 이러한 고속 스위칭에 의한 급격한 dv/dt 변화로 인해 발생한 커먼 모드 전 압은 모터 내부의 부유커패시터를 통하여 대지로 흐르는 고주파 누설전류의 발생과 베어링 전류, 축전압등을 발생시키며, 그 결과 전동기의 수명 저하, 절연 파괴, 전도, 방사 EMI(Electromagnetic Interference) 발생 등의 문제를 발생시킨다<sup>[1]-[4],[13]-[15]</sup>

커먼 모드 전압을 저감하는 방법을 크게 나누면 하드웨어적인 방법과 소프트웨어적인 방법이 있다 하드웨어적인 방법으로는 EMI필터 등을 삽입하여 커먼 모드 전압을 줄이는 방법이 있는데 이러한 경우에는 저감 대상이 변경 될 때마다 필터를 새로이 설계를 하여야 하며, 부피나 가격 등이 증가하게 되는 단점이 있다<sup>[5]-[7]</sup>.

소프트웨어적인 방법에는 PWM신호를 변경하는 방법이 있는데, 이러한 방법은 부가적인 하드웨어에 의한 부피나 가격 등이 증가되지 않고, 대상이 변경되어도 동일하게 적용이 가능하다는 장점이 있다<sup>[8]-[10]</sup>.

그러므로 본 논문에서는 부가적인 하드웨어 없이 PWM 신호를 변경하기 위하여 EPLD를 이용하여 120 도의 위상차를 갖는 3개의 삼각파 캐리어 발생 회로를 설계하여 전도노이즈 저감하는 방법을 제안하였다.

#### 2. PWM 인버터와 커먼 모드 전압

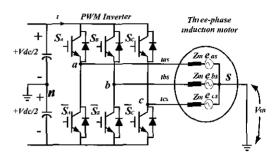

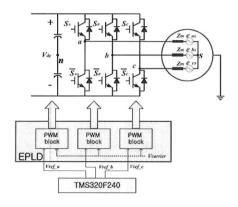

그림 1은 인덕터와 저항, 그리고 역기전력으로 모델 링된 전동기에 접속된 전압형 인버터를 보여주고 있다.

여기서 인버터의 전압 방정식은 다음 식과 같다

$$V_{as} = V_{an} - V_{sn} = Z_{m} i_{as} + e_{as}$$

$$V_{bs} = V_{bn} - V_{sn} = Z_{m} i_{bs} + e_{bs}$$

$$V_{cs} = V_{cn} - V_{sn} = Z_{m} i_{cs} + e_{cs}$$

(1)

여기서,  $V_{as}$ ,  $V_{bs}$ ,  $V_{cs}$ : 부하 상 전압  $V_{an}$ ,  $V_{bn}$ ,  $V_{cn}$ : 인버터 출릭 전압

1<sub>as</sub> , 1<sub>bs</sub> , 1<sub>cs</sub> · 전동기 상전류

$e_{as}$ ,  $e_{bs}$ ,  $e_{cs}$  전동기 역 기전력

$V_{sn}$  커먼모드 전압

Z., 전동기 내부 임피던스 이다

그림 1에서 식 (1)의 방정식을 더하면 식 (2)와 같이 유도된다

그림 1 인버터-유도전동기 구동시스템

Fig 1 Inverter-fed induction motor system

$$V_{an} + V_{bn} + V_{cn} - 3V_{sn}$$

$$= Z_m \cdot (i_{as} + i_{bs} + i_{cs}) + (e_{as} + e_{bs} + e_{cs})$$

(2)

전동기 부하가 평형일때의 3상 진류는 KCL법칙에 의해  $\iota_{as} + \iota_{bs} + \iota_{as} \cong 0$ ,  $e_{as} + e_{bs} + e_{as} \cong 0$  이므로 커먼 모드 전압은 식 (3)과 같이 정의 할 수 있다.

$$V_{sn} = -\frac{V_{an} + V_{bn} + V_{cn}}{3} \tag{3}$$

식 (3)은 단지 PWM 인버터의 스위칭 상태가 부하 임피던스에 상관없이 커먼 모드 전압  $V_{sn}$ 을 결정함 을 보여준다.

표 1은 인버터 스위칭 상태에 따른  $V_{sn}$ 의 변화를 나타내었다

스위칭 상태에 따라 인버터 출력전압은 2레벨을 갖으며, 커먼모드 전압은 부하상전압과 같이 4레벨을 갖느다

표 1 스위칭 상태에 따른 출력 전압과 커먼 모드 전압 Table 1 Output voltage and the common mode voltage by switching state

| 스위칭 상태          | 인버니 춝덕 진압   |                   |             | TZ.                    |

|-----------------|-------------|-------------------|-------------|------------------------|

| $(S_A S_B S_C)$ | $V_{an}$    | $V_{bn}$          | $V_{cn}$    | $V_{sn}$               |

| (0 0 0)         | $-V_{dc}/2$ | $V_{d\epsilon}/2$ | $-V_{dc}/2$ | $-V_{dc}/2$            |

| (1 0 0)         | $V_{dc}/2$  | $-V_{dc}/2$       | $-V_{dc}/2$ | $-\overline{V_{dc}}/6$ |

| (1 1 0)         | $V_{dc}/2$  | $V_{dc}/2$        | $-V_{dc}/2$ | $V_{dc}/6$             |

| (0 1 0)         | $-V_{dc}/2$ | $V_{dc}/2$        | $-V_{dc}/2$ | $-V_{dc}/6$            |

| (0 1 1)         | $-V_{dc}/2$ | $V_{dc}/2$        | $V_{dc}/2$  | $V_{dc}/6$             |

| (0 0 1)         | $-V_{dc}/2$ | $-V_{dc}/2$       | $V_{dc}/2$  | $-V_{dc}/6$            |

| (1 0 1)         | $V_{dc}/2$  | $-V_{dc}/2$       | $V_{dc}/2$  | $V_{dc}/6$             |

| (1 1 1)         | $V_{dc}/2$  | $V_{dc}/2$        | $V_{dc}/2$  | $V_{de}/2$             |

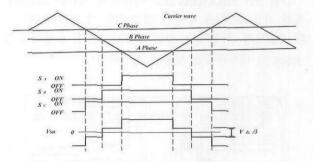

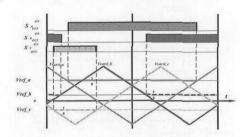

그림 2는 PWM 인버터의 스위칭 상태에 따른 커먼 모드 전압을 나타내었다.  $V_{sn}$ 은 스위칭할때 1/3  $V_{dc}$ 의 크기를 갖고 6스텝 형태로 변화함을 알수 있다.

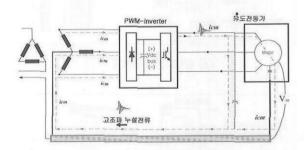

이와 같이 PWM 인버터에 의해 생성된 커먼 모드 전압  $V_{sn}$ 은 유도전동기 내의 고정자 권선과 고정자외함 사이에 존재하는 부유커패시터를 통해 접지단자로 흐르는 고주파 누설 전류  $i_{cm}$ 의 원인이 되고, 그경로는 그림 3과 같다 $^{[11]}$ .

그림 2 PWM 인버터의 스위칭 상태에 따라 생성된 커먼 모드 전압 및 게이팅 신호의 파형

Fig. 2 The waveforms of the gating signal and common mode voltage created according to switching state of PWM inverter

그림 3 PWM 인버터 구동 시스템의 누설전류 경로 Fig. 3 High frequency current path in the PWM inverter -fed induction motor system

# 3. 커먼 모드 전압을 저감하기 위해 제안된 스위칭 기법

# 3.1 종래의 정현파 PWM의 스위칭 기법

종래의 PWM 기법은 PWM 신호를 발생하기 위해 그림 4와 같이 120도 위상차를 갖는 정현파 기준 전압 을 삼각파 캐리어와 비교하였다. 본 논문에서는 종래 의 SPWM으로 나타내기로 한다.

그림 4 종래의 정현파 PWM의 스위칭 패턴

Fig. 4 Switching pattern of the conventional sinusoidal PWM

정현파 PWM에서 삼각파 캐리어의 한 주기동안 Duty는 정현파인 기준 전압에 의해 정해지고, 모두 같은 삼각파 캐리어를 사용하여 스위칭 함수가 정해진다.

따라서 3상의 스위칭 상태가 모두 같은 무효 벡터(0.00)와 (1.11)이 필연적으로 인가되게 된다. 즉 윗상의 스위치가 모두 온이거나 오프 상태일 때 커먼모드 전압이  $\pm V_{de}/2$ 이 된다.

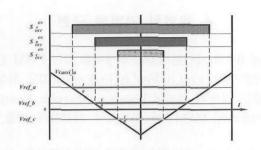

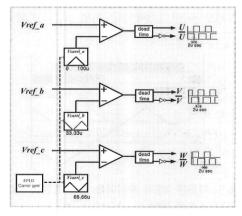

#### 3.2 제안된 정현파 PWM의 스위칭 기법

제안된 PWM에서는 3상의 스위칭 상태가 모두 같은 무효 벡터 성분을 제거하기 위해서 각각 120도의 위상 차를 갖는 3개의 삼각파 캐리어 Vcarri\_a, Vcarri\_b, Vcarri\_c와 3개의 정현파 Vref\_a, Vref\_b, Vref\_c를 비교하여 120도 위상차를 갖는 PWM파형을 만든다.

이와 같은 스위칭 기법을 통하여 한 주기 동안 무효벡터가 인가되는 것을 막을 수 있다. 따라서 커먼 모드 전압이  $\pm V_{dc}/2$ 되는 스위칭상태가 제거되므로 항상 커먼 모드 전압은  $\pm V_{dc}/6$ 로 제한된다. 즉, 종래의 SPWM보다 약 1/3배만큼 커먼 모드 전압을 저감된다.

그림 5 제안된 3개의 캐리어를 갖는 정현파 PWM의 스위칭 패턴

Fig. 5 Sinusoidal PWM pattern with the proposed three carrier waves

#### 4. 제안된 기법의 구현

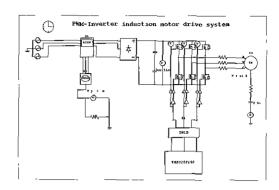

그림 6에서 제안된 120도 위상차를 갖는 PWM 신호는 기준 전압 Vref\_a, Vref\_b, Vref\_c와 120도 위상차를 갖는 삼각파 캐리어 Vcarri\_a, Vcarri\_b, Vcarri\_c를 이용하여 PWM발생 블럭에서 비교하여 만들 수 있다.

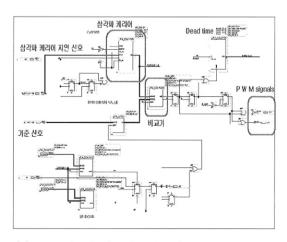

그림 7은 본 논문에서 제안된 PWM 구현은 Altera FLEX6000시리즈 EPLD에 구성된 캐리어 발생 블록에서 처리되어 120도 위상차를 갖는 삼각파 케리어 신호 (*Vcarri\_a, Vcarri\_b, Vcarri\_c*)를 발생시킨다.

이러한 캐리어는 기준전압 *Vref\_a*, *Vref\_b*, *Vref\_c*와 비교되어 각각의 PWM 신호가 발생되고 데드타임 블록을 거쳐 모터 구동을 위한 실질적인 PWM 파형이만들어진다.

구현된 PWM의 데드타임은 2 μsec 이다.

그림 6 PWM 인버터 유도전동기 시스템

Fig. 6 PWM inverter induction motor drive system

그림 7 제안된 PWM 발생 블럭 다이그램

Fig. 7 The proposed PWM genertion block diagram

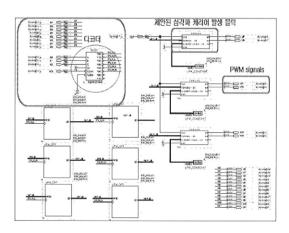

그림 8의 (a)는 EPLD의 전체 회로도이며, 디코더와 3개의 120도 위상차를 갖는 PWM 발생 블럭으로 구성되었다.

그림 8의 (b)는 120도 위상차를 갖는 PWM 발생 블 럭의 내부 회로도이다.

120도의 위상차를 갖는 3개의 삼각파 캐리어를 구현하기 위하여 3개의 업-다운 카운터 시작 시간을 지연하였고, 비교기 블럭에서 기준 전압과 각각의 삼각파캐리어를 비교한 후, 데드타임 블록을 거쳐 PWM신호를 발생하였다.

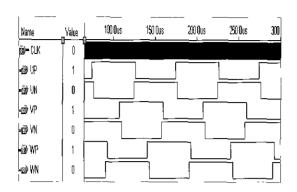

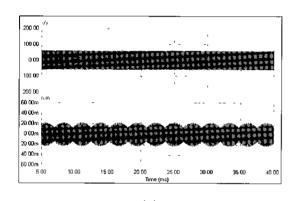

그림 9는 MAX+puls II를 이용하여 제안된 EPLD로 직의 시뮬레이션을 수행한 결과이며, 각 상(U,V,W) 마다 120도의 위상차를 갖는 PWM신호가 발생하고 2  $\mu$ sec의 데드타임을 갖음을 확인하였다.

(a) EPLD 전체구성도

(b) EPLD 내부회로(제안된 삼각파 캐리어 발생블럭)

그림 8 EPLD 구성도

Fig. 8 Sehematic block diagrams of EPLD

그림 9 제안된 EPLD의 시뮬레이션 파형 Fig. 9 Simulation result for EPLD

### 5. 시뮬레이션 결과

본 논문에서 제안된 스위칭 기법을 확인하기 위해 종래의 정현파 PWM 스위칭 방식과 제안된 스위칭 방식을 PSIM 50으로 시뮬레이션 하였다.

그림 10은 시뮬레이션 전체 회로도이며 전도 노이즈 를 측정하기 위한 스펙트럼 분석기, 인버터를 구동하 는 DSP, LISN(Line Impedance Stabilization Network), DMRN(Differential Mode Rejection Network)과 제안된 PWM를 발생하기위한 EPLD로 구 성되어있다

시뮬레이션의 EPLD 블록은 실제 EPLD와 동일하게 아날로그로 회로로 구성하였다

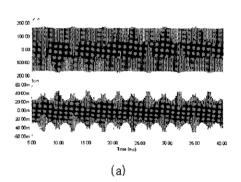

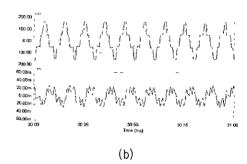

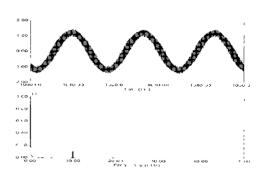

그림 11의 (a)는 종래의 PWM 스위칭 기법의 커먼 모드 전압과 전류의 전체 파형이며, (b)는 일부분을 확 대한 파형이다

$-V_{dc}/2 \le V_{sn} \le +V_{dc}/2$ 의 커먼 모드 전압 범위를 갖는다 커먼 모드 전류의 피크값은  $40 \mathrm{mA} \sim 50 \mathrm{mA}$ 이다.

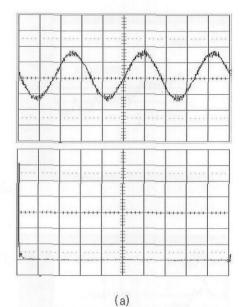

그림 12는 종래 스위칭 기법의 전동기의 한 상에대한 전류 파형과 FFT 분석한 결과를 보여주고 있다. 전동기 한 상의 FFT 분석 결과를 보면 스위칭 주파수 대역에서 고조파 성분이 보이고 있음을 알 수 있다

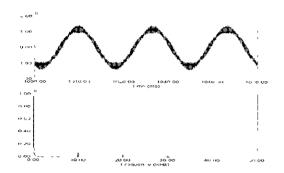

그림 13의 (a)는 재안된 스위칭 기법을 적용한 커먼 모드 전압과 커먼 모드 선류의 전체 파형이며, (b)는 일부분을 확대한 파형이다.

커먼 모드 전압의 범위는  $-V_{dc}/6 \le V_{sn} \le$

$+V_{dc}/6$  이고, 커먼 모드 전류의 피크 값은 20 mA가 흐르는 것을 볼 수 있다

그림 10 시뮬레이션 회로도 Fig 10 Simulation circuit diagram

그림 11 종래 스위칭 기법의 커먼모드 전압[100V/div] 및 커먼 모드 전류 파형[20mA/div]

Fig 11 Common mode voltage [100V/div] and current waveforms [20mA/div] of the conventional SPWM technique

결과적으로 영벡터 구간인 (0 0 0)이나 (1 1 1)이 제 거되므로 종래의 커먼 모드 전압 보다 약 1/3배 정도 줄어들었다

그림 13은 제안된 스위칭 기법에서의 전동기 한 상의 전류 파형과 FFT분석 결과를 보여 주고 있으며 그림 11과 비교하여 볼 때 10kHz에서 다소 증가함을 볼수 있다

그림 12 종래 스위칭 기법의 한상의 전류(위) [1A/dɪv] 및 FFT분석(아래) [0 2A/dɪv], [10Khz/dɪv]

Fig 12 A phase current waveform (upper)[1A/div] and FFT results (lower)[0 2A/div], [10Khz/div] of the conventional switching technique

(a)

그림 13 제안된 스위칭 기법의 커먼 모드전압 [100V/div]과 커먼 모드 전류 파형[20mA/div]

(b)

Fig 13 Common mode voltage[100V/div] and current waveforms[20mA/div] of the proposed switching technique

그림 14 제안된 스위칭 기법의 한 상의 전류(위) [1A/div] 와 FFT 분석(아래) [0 2A/div], [10KHz/div]

Fig 14 A phase current waveform (upper) and FFT results (lower) of the proposed switching technique

#### 6. 실험 결과

본 논문에서 제안한 스위칭 기법의 타당성을 입증하기 위하여 TMS320F240 DSP 보드와 3상 4국1735rpm, 22kW 유도 전동기를 무부하로 V/f운전 실험하였다. 표 2는 사용한 시스템 사양을 나타내었다

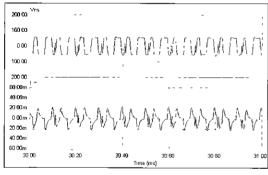

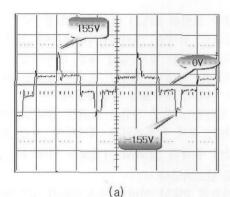

그림 15(a)는 종래의 PWM 방식으로 제어되는 3상 인버터의 커먼모드 전압  $V_{sn}$  의 파형이며, 이때 양의 peak값이 약 155V임을 알 수 있다 즉, 커먼모드 선압은 직류 링크단 전압의  $V_{dc}/2$ 이다

그림 15(b)에서는 제인된 PWM기법의 커먼모드 전압  $V_{sn}$ 의 실험 파형이며, 커먼 모드 전압  $V_{sn}$ 의 양의 피크 값은 약 52V이고, 직류 링크단 전압의  $V_{dc}/6$ 다. 이것은 시뮬레이션 파형과 일치함을 볼 수 있다

표 2 측정 시스템의 사양 Table 2 System specification

|                | · · · · · · · · · · · · · · · · · · ·                 |

|----------------|-------------------------------------------------------|

| 3 <b>Ø</b> 220 | V                                                     |

| 10             | kHz                                                   |

| 311            | V                                                     |

| DSP            | TMS320F240                                            |

| 000/000        |                                                       |

| 220/380        | V                                                     |

| 88/51          | A                                                     |

| 2.2            | kW                                                    |

| 1735           | rpm                                                   |

| 4              |                                                       |

|                | 10<br>311<br>DSP<br>220/380<br>8 8/5 1<br>2.2<br>1735 |

(b)

그림 15 커먼 모드 전압 파형

- (a) 종래의 SPWM [100V/div]

- (b) 제안된 SPWM [100V/div]

- Fig. 15 Common mode voltage waveforms

- (a) Conventional SPWM 100[V/div]

- (b) Proposed SPWM 100[V/div]

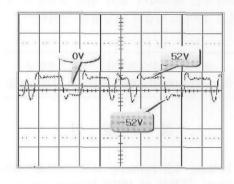

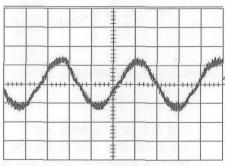

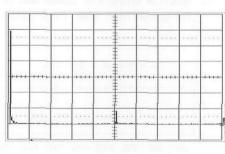

그림 16은 종래의 스위칭 기법과 제안된 스위칭 기 법의 상 전류와 FFT분석 결과이며 시뮬레이션과 동일 한 결과를 보여준다.

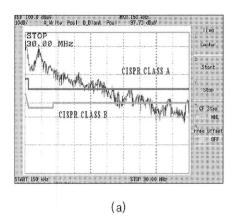

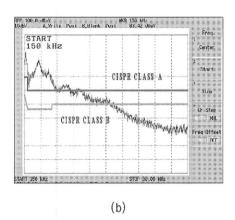

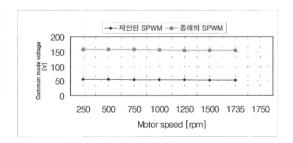

그림 17은 CISPR pub'#22 규제의 범위에서(150kHz ~30MHz) 노이즈의 스펙트럼 파형이며, 종래의 SPWM기법 보다 제안된 SPWM을 사용함으로 커먼 모드 전압의 크기가 줄어들어 전도 노이즈가 저감된 것을 확인 할 수 있다.

그림 18은 속도에 따른 커먼모드 전압 파형으로 전 동기 속도와 관계없이 커먼 모드 전압 크기는 종래의 SPWM을 사용할 때 약 155V정도이며, 제안된 SPWM 은 약 52V정도가 된다<sup>[12]</sup>.

따라서 실험에 사용된 전동기 구동시스템에 제안된 방법을 사용함으로써 약 103V 정도의 커먼 모드 전압 이 저감되는 효과를 얻을 수 있다.

(b)

그림 16 PWM 인버터 구동 유도전동기의 상전류 파형 (위) [1A/div] 및 FFT 분석 (아래) Ampere: [20mA/div] Time: [2kHz/div]

(a) 종래의 SPWM (b) 제안된 SPWM

Fig. 16 A phase current waveforms (upper) 1[A/div] and FFT results (lower) of the PWM inverter-fed induction motor

> Ampere: [20mA/div] Time: [2kHz/div] (a) Conventional SPWM (b) Proposed SPWM

그림 17 커먼 모드 EMI의 스펙트럼 파형

(a) 종래의 SPWM (b) 제안된 SPWM

Fig. 17 Spectrum waveform of common mode EMI

(a) Conventional SPWM (b) Proposed SPWM

그림 18 속도에 따른 커먼모드 전압 Fig. 18 Common mode voltage according to the speed

#### 7. 결 론

본 논문에서는 PWM 인버터에 의해 구동되는 유도 전동기 시스템에서 고주파 누설전류의 발생원인이 되 는 커먼 모드 전압을 저감하는 새로운 스위칭 기법을 제안하여 다음의 결과를 얻었다.

- 1) 실제 실험한 EPLD 블럭과 동일한 아날로그 로 직으로 삼각파 캐리어를 구현하여 시뮬레이션 하였다. 또한 실제 실험 대상 인버터에 적용하여 시뮬레이션에서 예측한 결과와 동일한 커먼 모 드 전압이 저감됨을 확인하였다.

- 2) 제안된 스위칭 기법은 스위칭 상태를 6개로 제한함으로써 무효벡터를 제거하여, 커먼 모드 전압이 종래의 SPWM 기법보다 약  $\pm V_{dc}/3$  정도 감소되었다.

- 3) 기존의 PWM 인버터 유도전동기 구동시스템에 추가적인 하드웨어 없이 쉽게 소프트웨어적으로 전도 노이즈 저감이 가능함을 보였다.

본 연구는 한국과학재단 목적기초연구 (R01-2001-000-00306-0) 지원으로 수행되었슴.

### 참 고 문 헌

- [1] J. Erdman, R.J. Kerkman, D.W. Schlegel, and G.L. Skibinski, "Effect of PWM Inverters on AC Motor Bearing Currents and Shaft Voltages", IEEE Trans. Ind. Appl., vol. 32, pp. 250~259, Mar/Apr. 1996.

- [2] E. Zhong and T.A. Lipo, "Improvements in EMC Performance of Inverter-Fed Motor Drives", IEEE Trans. on Ind. Appl., vol. 31, pp. 1247~1256, Nov/ Dec. 1995.

- [3] S. Ogasawara and H. Akagi, "Modeling and Damping of High-Frequency Leakage Currents in PWM Inverter-Fed AC Motor Drive Systems", IEEE Trans. Ind. Appl., vol. 32, pp. 1105~1114, Sep/Oct. 1996.

- [4] M.A. Cash and T.O. Habetler, "Insulation Failure Prediction in Inverter-Fed Induction Machines Using Line-Neutral Voltages", IEEE APEC Conf., pp. 1035~ 1039, 1998.

- [5] Rendusara, D. Enjeti, P., "New Inverter Output Filter Configuration Reduces Common Mode and Differential Mode dv/dt at the Motor Terminals in PWM Drive Systems", PESC '97 Record, vol. 2, pp. 1269~1275, 1997.

- [6] Lee-Hun Kim, Hwan-Kyun Yun, Chung-Yuen Won, Young-Real Kim, and Gi-Su Choi, "Output Filter Design for Conducted EMI Reduction of PWM Inverter-fed Induction Motor System", Power Electronics and Drive Systems, 2001 4th IEEE Int'l. Conf. on., vol. 1, pp. 252~258, Oct. 2001.

- [7] Hwan-Kyun Yun, Yuen-Chung Kim, Chung-Yuen

- Won, Young-Ryul Kim, Young-Seok Kim, and Se-Wan Choi, "A Study on Inverter and Motor Winding for Conducted EMI Prediction", Proceedings on ISIE 2001, vol. 2, pp. 752~758, 2001.

- [8] M. Cacciato, A. Consoli, and G. Scarcella, "PWM to Square Wave Inverter Control with Low Common Mode Emissions", PESC '98 Record, vol. 1, pp. 871~ 877, 1998.

- [9] Yen-Shin Lai, "Investigations into The Effects of PWM Techniques on Common Mode Voltage for Inverter-Controlled Induction Motor Drives", Power Engineering Society 1999 Winter Meeting, IEEE., vol. 1, pp. 35~40, 1999.

- [10] M. Cacciato, C. Cavallaro, A. Consoli, G. Scarcella, and A. Testa, "A Comparative Analysis of High Frequency Currents Generated by Pulse width Modulation Techniques", Electric Machines and Drives, 1999, Int'l. Conf., pp. 698~700, 1999.

- [11] A. von Jouanne and P. Enjeti, "Application Issues for PWM Adjustable Speed AC Motor Drives", IEEE Industry Applications Magazine, pp. 10~18, Sep/Oct. 1996.

- [12] Hyeoun-Dong Lee and Seung-Ki Sul, "Common-Mode Voltage Reduction Method Modifyin the Distribution of zero-voltage Vector in PWM Converter/Inverter system", IEEE Trans. on Industry Appl., Vol. 37, pp. 1732~1738, Nov/Dec. 2001.

- [13] 이진환, 안정준, 원충연, 김영석, 최세완, "PWM인버터-유도전동기 구동시스템의 전도노이즈 예측", 전력전자학 회 논문지, 제4권 6호, pp. 579~588, 1999.

- [14] 김이훈, 박규현, 원충연, 김영석, 최세완, "PWM 인버터 시스템에서의 전도노이즈 저감을 위한 출력필터 설계에 관한 연구", 전력전자학회 논문지, 제6권 6호, pp. 546~555, 2001.

- [15] 위석오, 정영국, 나석환, 임영철, "모터 구동 장치의 가청 스위칭 소음 저감을 위한 2상 및 3상 렌덤 펄스 위치 PWM기법의 성능 비교", 전력전자학회 논문지, 제7권 3호, pp. 224~236, 2002.

#### 저 자 소 개

# 박규현(朴奎炫)

1975년 2월 10일생. 2001년 서울산업대 전기공학과 졸업. .2002년 성균관대학교 대학원 메카트로닉스공학과 졸업(석사). 현재 LG전자 연구원.

#### 김이훈(金利勳)

1970년 7월 7일생. 1999년 충주대 제어계 측공학과 졸업. 2001년 성균관대 대학원 메카트로닉스공학과 졸업(석사). 2003년 현재 동 대학원 메카트로닉스공학과 박사과정.

#### 원충연(元忠淵)

1955년 5월 10일생. 1987년 서울대 대학원 전기공학과 졸업(공박). 1997년 12월~ 1992년 12월 미국 테네시 주립대학 전기공학과 방문교수. 1988년 3월~현재 성균관대학교 정보통신공학부 교수. 당 학회부회장.

#### 김규식(金奎植)

1958년 8월 25일생. 1981년 서울대 전자 공학과 졸업. 1983년 동 대학원 제어계측 공학과 졸업(석사). 1990년 8월 동 대학원 제어계측공학과 졸업(박사). 1988년~1992 년 대우중공업 중앙연구소 선임연구원. 1993년~현재 서울시립대학교 전기전자 컴퓨터공학부 부교수.

#### 최세완(崔世琓)

1963년 3월 3일생. 1985년 인하대 전자공학과 졸업. 1992년 Texas A&M Univ. 전기공학과 졸업(석사). 1995년 동 대학원졸업(박사). 1996년~1997년 삼성전기 종합연구소 수석연구원. 1997년~현재 서울산업대 제어계측공학과 조교수. Journal

of Electrical Engineering and Information Science 편집위원. 당 학회 편집위원.

#### 함년근(咸年根)

1970년 3월 2일생. 1996년 명지대 전기공학과 졸업. 1998년 동 대학원 전기공학과 졸업(석사). 1998년~현재 동 대학원 박사과정. 현재 인텍 FA 전력전자연구소 선임연구원.